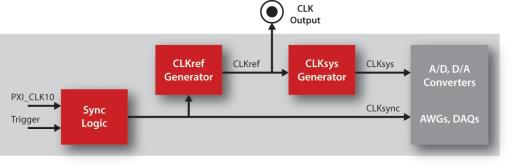

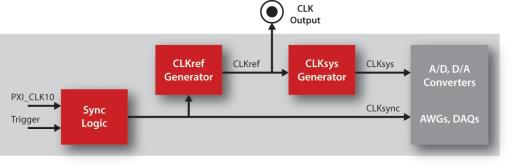

The M31/M33XXA Digitizers uses an internally generated high-quality clock (CLKref) which is phase-locked to the chassis clock. Therefore, this clock is an extremely jitter-cleaned copy of the chassis clock. This implementation achieves a jitter and phase noise above 100 Hz which is independent of the chassis clock, depending on it only for the frequency absolute precision and long term stability. A copy of CLKref is available at the CLK connector (Table 13).

CLKref is used as a reference to generate CLKsys, the high-frequency clock used to sample data.

| Programming Definitions | |||

|---|---|---|---|

|

Option |

Description |

Name |

Value |

|

Disable |

The CLK connector is disable

|

n/a |

0 (default) |

| CLKref Output | A copy of the reference clock is available at the CLK connector | n/a | 1 |

Table 13: M31/M33XXA Digitizers output clock configuration

The sampling frequency of the M31/M33XXA Digitizers (CLKsys frequency) can be changed using the advanced clocking system shown in Figure 7.

Figure 7: Functional diagram of the M31/M33XXA Digitizers FlexCLK system

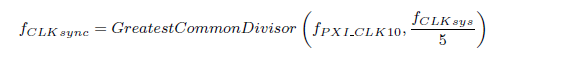

where:

The CLKsys frequency can be changed within the range indicated in the datasheet of the corresponding product (function clockSet- Frequency, Section 2.3.4.17 on page 44). The CLKsync frequency changes with the CLKsys frequency as follows:

The CLKsync frequency is returned by the function clockSetFrequency

| Programming Definitions | |||

|---|---|---|---|

|

Option |

Description |

Name |

Value |

|

Low Jitter Mode |

The clock system is set to achieve the lowest jitter, sacrificing tuning speed |

CLK_LOW_JITTER |

0 |

|

Fast Tuning Mode |

The clock system is set to achieve the lowest tuning time, sacrificing jitter performance |

CLK_FAST_TUNE |

1 |

Table 14: Clock set frequency mode (function clockSetFrequency